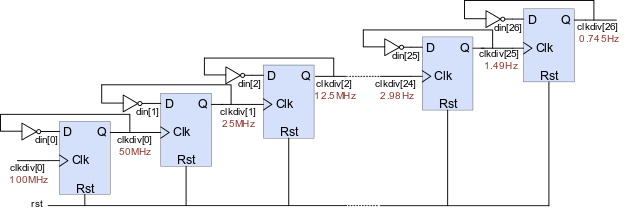

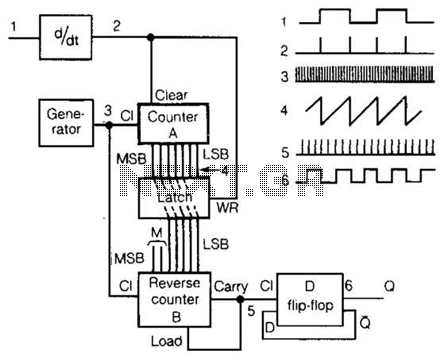

Design of an All-Digital Synchronized Frequency Multiplier Based on a Dual-Loop (D/FLL) Architecture

Design of an All-Digital Synchronized Frequency Multiplier Based on a Dual-Loop (D/FLL) Architecture

Design of an All-Digital Synchronized Frequency Multiplier Based on a Dual-Loop (D/FLL) Architecture

![PDF] Phase Locked Loop Design as a Frequency Multiplier | Semantic Scholar PDF] Phase Locked Loop Design as a Frequency Multiplier | Semantic Scholar](https://d3i71xaburhd42.cloudfront.net/cf813672ef027c5b17c3a859b7a57d2722551267/24-Figure12-1.png)